# Report for Phase 3 2001-2003

UPPSALA UNIVERSITY

## **ASTEC: Advanced Software Technology**

## Report for the Third International Evaluation (covering the period 2001 – 2003)

## Introduction

This document reports on the activities of the competence centre Advanced Software Technology (ASTEC) during the period 2001-2003, in preparation for its Third International Evaluation on September 8 and 9, 2003. The structure of the document follows the <u>guidelines</u> given by VINNOVA. Up-to-date information about current activities of ASTEC can be found on the WWW page <u>http://www.astec.uu.se/</u>.

## Contents

- Executive Summary

- Basic Facts

- A. Technical Results and Scientific Outputs

- A.1. Research Programme

- A.2. Technical and Scientific Achievements

- A.3. Scientific Papers

- A.4. Examinations

- A.5.Education and Training

- B. Standing of the Competence Center in an International and National Context

- B.1. Progress of the Centre in Relation to its Long-Term Goals

- B.2. International and National Collaboration

- B.3. Core Competences and Critical Mass

- B.4. Role and Impact of the Centre within the University

- B.5. Future Plans and Strategies

- C. Industrial Benefits, Technology Transfer, Impact to the Industrial Partners

- C.1. Industrial Involvement and Interaction

- C.2. Ways to Facilitate Industrial Implementation

- C.3. Commercialisation and Technology Transfer

- C.4. Success Stories

- C.5. Impact on the Industrial Partners

- D. Future Plans and Strategies

- <u>Appendices</u>

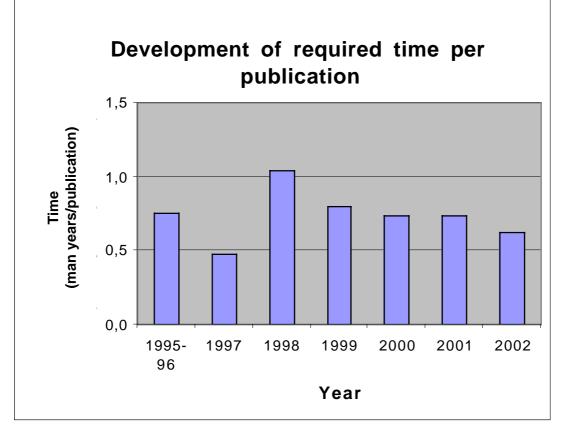

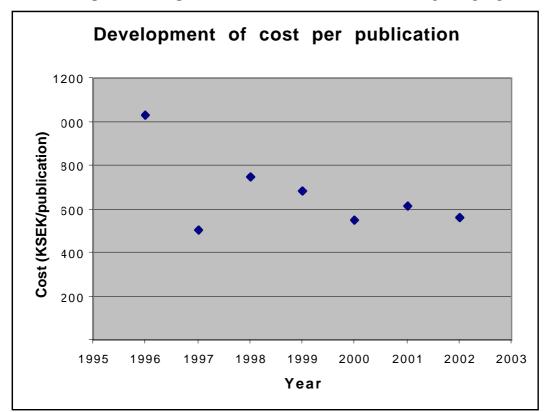

- 1. ASTEC Business ratios 1995-2002

- 2. Partners

- 3. Research staff 1995-2003

- 4. Financial report

- Account for income, budget and economic result for 2001-2003 as (PDF)

- 5. Industrial partners statements

- 6. Projects

- 7. Publications

- 8. ASTEC scientific advisors report 2003 as pdf

- 9. Evaluation report 00-09-28 as pdf

- 10. <u>Curricula vitae for Directors of ASTEC Bengt Jonsson and Konstantios</u> <u>Sagonas</u>

## **Executive Summary**

ASTEC (Advanced Software Technology) is a competence centre which focuses on advanced tools and techniques for software development. Development of software accounts for a significant part of the costs in the construction of a number of important products, such as communication systems, transportation and process control systems, of Swedish industry. It is thus a vital interest to be able to produce better software at lower cost. One of the means to achieve this is to improve the tools and techniques used for software development. ASTECs vision is that, wherever possible, software should be developed using high-level specification and programming languages, supported by powerful automated tools that assist in specification, analysis, validation, simulation, and compilation. The purpose of ASTEC is to conduct pre-competitive and industrially applicable research that contributes to this vision, to build up and offer a concentrated research environment in the software technology area, and to be a forum for contacts and exchange of ideas between academia and industry.

ASTEC has been formed as a consortium of academic partners with strong research programs in different areas of software technologies, and of companies which either have a substantial software production or produce tools for software development. During its first two years, ASTEC conducted projects where techniques from academia were applied to problems in industry, resulting in the creation of a network of contacts between academia and industry. In its second phase, guided by a strategic plan, a research environment with critical mass and a clear profile and competence on highest international level in key strategic areas has been built. In the current phase, ASTEC has focussed on technology transfer of sufficiently mature projects, and on developing tools that can solve significant industrial development problems.

Currently, ASTEC has developed into a focussed and distinct research unit, having a broad contact area with a number of companies. It is a natural forum for collaboration, discussions, and new contacts in the software technology area. Some of the main results of ASTEC work can be summarized as follows.

- ASTEC has consolidated its critical mass and competence on highest international level in key strategic areas. The production of interesting and recognized research results has continued. A sign of recognition is that centre groups participate in an increasing number of European collaboration projects.

- The number of industrial partners of ASTEC has been steadily increasing. Results from ASTEC work have been transferred and are used in industry. Some of the technology development in ASTEC has been transferred into industrial products, which are currently supported by ASTEC groups. The academic-industrial collaboration has given ASTEC research very valuable access to industrial software for experimentation, evaluation, and code development, as well as a rich source of interesting research problems.

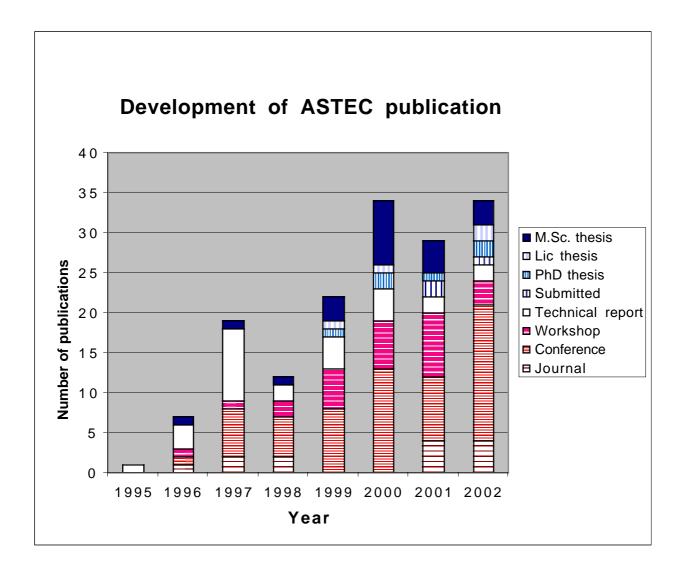

- The production of Ph.D., Lic., and M.Sc. graduates has continued. The centre contributes courses to national and local graduate and undergraduate education. Several tools produced in ASTEC work are used in graduate and undergraduate education, both locally, nationally, and internationally.

In the next phase, ASTEC intends to consolidate its work from the industrial and application perspective, as well as investigate interesting new concepts in software technology. Mature tools will continue to be developed, prototype tools should become industrially usable and integrated, and projects that are still preliminary should use industrial examples as a major focus. ASTEC will also promote the industrial uptake of techniques that it has developed.

The existing developed tools will also serve as a basis for continued investigation of new interesting concepts in software technology. Greater interaction between other researchers in Europe working on similar topics or projects is strongly desirable. ASTEC researchers will continue the trend of increasing participation in European collaboration activities.

ASTEC will continue its development of upper-level undergraduate courses, and also further develop the role of ASTEC tools for educational purposes.

## **Basic Facts**

ASTEC is formed as a consortium of the following academic and industrial partners.

- Research groups at *Uppsala University*, the *Swedish Institute of Computer Science* (SICS), and *Mälardalen University*, working mainly on formal methods, functional, logic and constraint programming languages, compilation, and on embedded, distributed, and real-time systems, together with

- companies with a substantial software production and thus a large interest in software development: *ABB Ltd, Cross Country Systems AB, Ericsson AB, ESAB Welding Equipment AB, T-mobile Inc, Validation AB,* and *Volvo Technological Development Corporation,* and companies that produce tools for software development: *IAR Systems AB, Mobile Arts AB, OSE Systems AB, Prover Technology AB, Telelogic Sverige AB, Virtutech AB* and *Volcano Communication Technologies AB.*

Further details about the partners, about accounting, economic details, and staff are given in Appendix 1-4. A notable figure is that since 1995 the number of companies has grown from 6 to 14 which corresponds to adding one company per year.

#### Management

The management of ASTEC is structured as follows:

- Within Uppsala University, ASTEC is a separate financial unit, hosted by the Department of Information Technology. All personnel involved in ASTEC are employed by the participating institutions and companies.

- ASTEC Activities are controlled by a board, whose ordinary members are currently Bjarne Däcker (Chairman), Martin Eriksson (Validation AB), Catrin Hansson-Granbom (Ericsson AB), Olle Landström (IAR Systems AB), Jan Lindblad (OSE Systems AB), Erik Hagersten (Uppsala University), and Björn Lisper (KTH/Mälardalens högskola).

- Daily management is performed by the director, Bengt Jonsson, the assisting director, Konstantinos Sagonas, the administrative research coordinator Roland Grönroos, and the respective project coordinators. The directors and project coordinators have regular monthly meetings.

- Area coordinators for each technical area are responsible for strategic project planning and for planning seminars. Longer-term project planning and progress is supervised by the Scientific Advisory board, consisting of Neil Jones, Bernhard Steffen, and Neeraj Suri, which conducts yearly internal reviews.

- All funding decisions are taken by the board. The board follows activities through project reports every 6 months, and contributes to ensuring the industrial relevance of ASTEC work.

The scientific work in ASTEC is carried out in cooperation between the participating research groups, both in industry and academia. There are many informal links, discussions, and technical links between projects within ASTEC. Formal components in this cooperation are the *ASTEC seminar series*, which typically meets twice a month, and regularly organized *program area seminars*. Two-day workshops for the entire ASTEC are conducted annually. The last ones have been conducted at Sätra Brunn in 1997, at Skokloster in 1999, at Fagerudd in 2000 and 2002, at Bergby gård in 2001, and at Oscar II in Uppsala in 2003.

## A. Technical Results and Scientific Outputs

## A.1. Research Programme

The research activities of ASTEC are structured into *programme areas*, which focus the efforts from several projects and are responsible for a wider dissemination of the conclusions, conducting seminars or specialised courses as deemed necessary. The areas are interrelated in that progress in one area is influenced and often driven by the state of the art in the others.

Each program area is either an *application* area, which provides problems to drive the research, or a *technical* area in which techniques, tools, and methods are developed. A particular project can very well span over several of these areas, and typically belongs in at least one technical area and one application area.

The application areas are:

- Software for data- and telecommunication systems, with requirements on mobility, high distribution, massive concurrency, and code replacement without disruption of the continuous operation of the system.

- **Software for embedded applications**, including safety-critical software, often deployed on a distributed network.

The technical areas are

- Validation and verification is concerned with high-level notations for expressing requirements and design specifications, together with tools and (formal) methods for analysis of specifications for the purposes of verification, validation, test generation, and tracing of requirements.

- **Programming language implementation and compilation** is concerned with the implementation and use of high-level (concurrent) programming languages, together with the development of compilation technology for (time- or space-) efficient program execution and code generation for different architectures.

- Real-time, embedded, and distributed systems is an area concerned with features specific to software development for real-time, embedded, or distributed systems, such as predictability, timeliness, scheduling, and distribution.

The application areas and technical areas form a  $2^{*3}$  matrix. which is used to structure projects. Table 1 shows acronyms of the projects that have been conducted during 2000 - 2003.

|                                           | Validation and<br>Verification                            | Programming<br>Languages and<br>Compilation | Real-Time<br>Distributed<br>Systems       |  |

|-------------------------------------------|-----------------------------------------------------------|---------------------------------------------|-------------------------------------------|--|

| Data- and<br>Telecommunication<br>Systems | BUS EnVer<br>SA SMC<br>Testing<br>Remodeling              | HiPE<br>Failure Analysis<br>SA              | BUS<br>HiPE<br>Remodeling                 |  |

| Embedded<br>Applications                  | Auto BUS<br>SAAPP<br>Software synthesis<br>SMC<br>Testing | WCET<br>WPO                                 | Auto<br>Software synthesis<br>TAS<br>WCET |  |

Table 1. ASTEC projects per programme area during 2000 - 2003.

At the time of the previous evalution, in year 2000, the following projects were conducted.

- Auto: A design methodology for embedded real-time systems

- BUS: Modeling and analysis of a bus protocol

- ErlVer: A Verification Method for Erlang

- HiPE: High Performance Erlang

- SA: Analysis of types and process topology for static debugging

- SMC: Symbolic Model Checking

- Testing: Automated Testing

- WCET: Calculation of Worst-Case Execution Times

• WPO: Whole-Program Optimization in Compilers for Embedded

Of these, the projects Auto, BUS, and SA were completed at the end of year 2000. The project ErIVer was completed in the summer of 2001. The projects HiPE, SMC, Testing, WCET, and WPO are still ongoing.

During the current period (2001-2003), the following projects have been initiated

- Failure Analysis: Static analysis of recovery propertes of Erlang applications

- Remodeling: Reverse engineering of industrial real-time applications

- SAAPP: Simulator-Aided Analysis of Parallel Processes

- Software Synthesis Guaranteeing Timing Constraints

- TAS: Time-Accurate Simulation

Of these, **Failure Analysis** and **TAS** have concluded, while the remaining ones (**Remodeling**, **SAAPP**, and **Software Synthesis**) will continue into the next phase of ASTEC. In addition, the umbrella **CODER**: Cluster on Distributed Embedded Real-Time Systems, encompassing the **TAS**, **WCET**, and **WPO** projects, has been formed in 2001.

Short descriptions for each project can be found in Appendix 6.

## A.2. Technical and Scientific Achievements

The presentation of the achievements are structured according to area. We first consider the two application areas followed by the three technical areas.

#### **Application Areas**

#### A.2.1. Software for Data- and Telecommunication Systems

ASTEC's vision is that development of communications software should be conducted, not by large organisations employing heavy and often old-fashioned software development processes, but by small, well-qualified teams working with powerful development tools that enable them to quickly turn an innovative idea into a products. This means that the tools should preferably embody solutions to typical requirements for these systems, including reliability, massive concurrency, ability to update systems with new functionality while in operation *etc*.

In this respect, an ASTEC project has been actively involved in the development of the *Erlang* programming language and several projects have centered around applications written in Erlang. Erlang is a concurrent functional programming language designed by Ericsson to ease the development of large-scale, distributed, soft real-time applications. Erlang has thus far been used quite successfully in the telecommunication industry, both within Ericsson Telecom, where it was designed and developed, and by other companies (both within Sweden and internationally). Examples of product whose software is written in Erlang are scalable ATM switching systems, ADSL delivery systems, next-generation call centers, scalable internet servers, mail robustifiers *etc.* ASTEC's involvement in the context of Erlang has spanned various aspects of Erlang's design, implementation, and use:

- at the level of programming language design, two significant extensions of the Erlang language (a package system and a parameterized module system) have been designed and implemented in the context of the **HiPE** (High Performance Erlang) project;

- at the level of the efficient implementation of the language, the HiPE native code compiler and a shared heap runtime system architecture have been developed and fully incorporated within the Erlang/OTP (Open Telecom Platform) system;

- at the level of enhancing the robustness and safety of applications, tools that aid the verification and testing of applications written in Erlang have been developed in the context of the ASTEC projects **ErlVer** (Erlang Verification), **Failure Analysis**, and **Testing**.

We describe these software tools below.

The major goal of the **HiPE** project has been to improve the performance characteristics of Erlang applications through better implementations of the language. In the previous period of ASTEC, the main means to achieve this goal was through the development of a native code compiler for Erlang. A native code compiler with a SPARC back-end was developed and open-source released as an autonomous system, called the *HiPE system* in March 2000.

Aiming to achieve more impact on the Erlang community, during the current period of ASTEC, the major goal of the **HiPE** project has been the full incorporation and integration of the HiPE native code compiler in the Erlang/OTP system from Ericsson (which is the most commonly used implementation Erlang, and certainly the only system used in commercial applications). This goal is now fully accomplished. It has been achieved in three steps:

- 1. First, HiPE was ported to the then latest Erlang/OTP implementation (Release 7B-1). This step was completed in February 2001.

- 2. Since then, a much closer co-operation between the HiPE team and the Erlang/OTP team from Ericsson was established through common day-long meetings every 2-3 months, and a very frequent exchange of code snapshots (almost every night). This co-operation has resulted in incorporating HiPE into the main branch of the Erlang/OTP development and the HiPE compiler was finally released as part of the open source Erlang/OTP R8B (October 2001).

- 3. Finally, since experience from using HiPE compiler in the Erlang user community was positive, a decision was made to have HiPE as a fully integrated and supported component in Erlang/OTP R9B (October 2002) and R9C (August 2003). This refers to both the open source and commercial versions of Erlang/OTP.

In addition to porting the HiPE compiler in Erlang/OTP, a sub-project within the **HiPE** project developed an alternative runtime system architecture for the Erlang/OTP system. Its main characteristic is the use of a shared heap space for all Erlang processes, which enables inter-process communication to occur with significantly less costs. This work, which is fully described in a Section A.2.4 of this report, is nowadays also fully integrated within the Erlang/OTP system (starting with R9B). More information can be found at <u>Erlang/OTP's homepage.</u>

The HiPE compiler improves the performance of Erlang applications from a few percent up to an order of magnitude. Furthermore, significant space improvements (e.g. an order of magnitude reduction) from uses of the shared heap runtime system architecture can often be observed in large, highly concurrent Erlang applications (e.g. in the *NETSim* product from Ericsson). Feedback from users of features of Erlang/OTP developed in the context of the **HiPE** project is quite positive. As a concrete example, in 2003, another company, T-Mobile, joined ASTEC as a new industrial partner and became the second industrial partner of the **HiPE** project (the first being Ericsson).

Software for telecommunication systems often possesses certain characteristics, such as massive and dynamic concurrency and on-line updating of software, that prohibit the use of fully automatic verification techniques. To permit verification of such software programmed in Erlang a major effort has been undertaken in the **ErlVer** project, which was conducted mainly in the previous period of ASTEC and concluded during 2001. A significant part of the work is described in the Ph.D. Thesis of Lars-åke Fredlund (Sept. 2001). An operational semantics for Erlang has been developed, with a property specification language and a novel proof system for compositional and inductive reasoning. To support verification, a proof assistant with a state-of-the-art graphical user interface and considerable support for proof automation is available: the Erlang Verification Tool (EVT). The feasibility of the method has been illustrated in case studies such as, e.g., the verification of a core part of the Mnesia distributed database system which is part of the standard Erlang distribution. As a side effect of the Erlang verification effort, two patent applications at Ericsson's Computer Science Laboratory were indirectly stimulated.

The EVT tool is rather ambitious, in that it allows to verify arbitrary properties of the

behavior of an Erlang program, which could be expressed in a general property language. As a consequence, it is difficult to obtain automatic proofs for properties of programs of significant size. A comment of the previous ASTEC evaluation was to "adopt more realistic goals". In response, in the current period, 2001–2003, two new – and smaller – ASTEC projects have been initiated aiming at the automated validation and testing of certain characteristics of typical applications written Erlang.

More specifically, the **Failure analysis** project differs from the **ErlVer** project in that its purpose is to develop a tool which focuses on analyzing only the failure behavior of a telecom application, but which in return is able to do so fully automatically on applications of significant size. The techniques developed in the context of this project analyze what is the effect of a process failure on the overall system and how the system can recover from such a failure. These techniques crucially assume (and also check) that the programmer has used the built-in support for failure recovery that is provided by the Erlang/OTP platform. The tool has been evaluated on several parts of the software in the AXD 301 switch.

Another automated tool for analyzing the behaviour of telecom applications written Erlang is currently being developed in the **Testing** project in collaboration with the company MobileArts. The tool allows the automatic generation of test sequences for telecom protocols. The generation considers both control and data aspects of the protocol; data parameters are handled symbolically. The tool assumes that the protocol to be tested is specified as a state machine, and generates a test suite. The tool is currently applied to a product under development within MobileArts, for which it is possible to achieve a very high degree of coverage.

#### A.2.2. Software for Embedded Applications

A lot of effort is currently devoted to developing and formalizing a complete methodology for building software in embedded systems, for instance within the automotive industry. Such a methodology should cover the entire chain from requirements to running code on a specific target platform. Systems are often assembled from parts delivered by subcontractors, and requirements on resource consumption are often very stringent. Challenging research problems include development of notations for requirements, techniques for system modeling and for analyzing whether a component or a collection of components conforms to requirements, techniques for mapping a design onto a distributed target architecture, and for generating code which satisfies requirements on memory, power and timing consumption.

Since its start, ASTEC has addressed several of these research challenges in case studies, technical research work, and tool development. A focus during 2001-2003 has been the development of tools that address larger chunks in the development chain by combining solutions to several related problems. Two major efforts in this area are the TIMES tool, which combines modeling, schedulability analysis, schedule synthesis, and code synthesis, and the development of an integrated tool for calculating the WCET (Worst-Case Execution Time) of embedded programs.

TIMES is a tool for Modeling and Implementation of Embedded Systems, which supports modelling, simulation, verification, schedulability analysis, synthesis of (optimal) schedules and executable code. It is appropriate for systems that can be described as a set of tasks which are triggered periodically or sporadically by time or external events. Currently TIMES supports code generation for the LegoOS platform. A system model consists of three parts: a control part represented as a network of timed automata extended with tasks, parameters of the triggered tasks, and a scheduling policy. The unique feature of TIMES is that it supports a more general process model (timed automata) than usual in classic scheduling theory, where processes are usually assumed to be periodic. The schedulability analysis then avoids overly pessimistic results, made possible by exploiting recent advances in verification of timed systems, as embodied in UPPAAL. A description of technical advances is contained in Section A.2.3. The TIMES tool received the Best tool award at the ETAPS conferences in April 2002.

The **WCET** project has, by June 2003, produced an end-to-end prototype tool that takes a C program as input and automatically generates a WCET estimate for the program. The aim is to make the WCET calculation (almost) fully automatic, thus relieving the programmer from the burden of current practice to annotate the program with flow information, and to measure (by testing or simulation) the execution time of individual code segments.

The prototype tool integrates solutions to all parts of the WCET problem puzzle: it compiles the program and generates a representation of its structure, it makes a semantic analysis of the program code and generates flow information that states how many times each part may be executed, it analyzes the effects of low-level processor features, such as caches and pipelines, and finally it combines all the information to calculate the actual WCET of the program. The tool is built on the modular tool architecture developed within the WCET project for combining modules that solve each particular subproblem into an end-to-end tool. In Section A.2.5, we describe how research performed within ASTEC has contributed to addressing each of these technical problems.

The quality of the results generated by the WCET tool are very competitive. For the classes of processor addressed by the pipeline analysis, very tight results have been demonstrated. The flow analysis gives good flow information for simple programs, and is continually being extended to handle greater parts of the C language. Thanks to working within a compiler, very powerful analyses are possible which are much harder for an approach that starts from the object code.

An industrial case study has been performed together with Enea OSE to assess the real-life usefulness of a WCET tool. The results indicated that there were significant benefits to be obtained from such a tool. The case study also indicated several practical details that need to be solved in order to produce a generally useful WCET tool. The work on gathering industrial requirements for WCET tools, which started with a questionnaire and interview survey in 1997, has been continued at the European level within the ARTIST iniative.

In cooperation with CC Systems, the **TAS** (Time-Accurate Simulation) project has (in a series of M.Sc. theses) developed techniques to simulate distributed real-time systems in real time, in order to allow efficient testing and debugging on a regular PC. They have been proven by use in industrial pilot studies together with customers of CC-Systems, and are being used today at CC-Systems to develop new embedded control systems. TAS is a good example of how the university world can help small companies adopt and develop simple but powerful ideas into techniques that confer concrete competitive advantages.

Timing properties are also central for the **Remodeling** project, conducted in cooperation with ABB Robotics, but this project has a different goal, namely to develop techniques to recover the structure of old, complex, real-time software, in order to allow easier maintenance and addition of new functionality, also by third parties. The project uses measurements to generate a model of an existing system that covers resource usage of programs, such as timing properties, memory consumption, and performance properties.

#### **Technical Areas**

#### A.2.3. Validation and Verification Technology

The area considers methods and tools for specifying and analysing properties of the behavior of systems and system components. The emphasis is on formal approaches to requirement and design specification, and on methods and tools for establishing adherence of systems to their specifications.

During 1999-2000, several industrial case studies were carried out, in which industrial protocols and distributed software systems were verified using existing verification tools, such as UPPAAL. Verification is carried out on a *model* of the system, the creation of which is a significant effort. It is not reasonable to expect that industrial software development develops both a software system and a model of it as separate activities.

Moreover, it is a challenge to develop executable code from such models with predictable timing behaviours. Main research issues include schedulability analysis and schedule synthesis. The **Software Synthesis** project was created in 2000 to develop the TIMES tool, which is designed for schedulability analysis and generation of executable code with predictable timing behaviour from design models that can be analyzed by UPPAAL. The TIMES tool is based on UPPAAL, but also incorporates our recent results on schedulability analysis.

In classic scheduling theory, real time tasks (processes) are usually assumed to be periodic, i.e. tasks arrive (and will be computed) with fixed rates periodically. Analysis based on such a model of computation often yields pessimistic results. To relax the stringent constraints on task arrival times, we have proposed to use automata with timing constraints to model task arrival patterns. This yields a generic task model for real time systems. The model is expressive enough to describe concurrency and synchronization, and real time tasks which may be periodic, sporadic, preemptive or non-preemptive, as well as precedence and resource constraints. We believe that the model may serve as a bridge between scheduling theory and automata-theoretic approaches to system modeling and analysis. The standard notion of schedulability is naturally generalized to automata. An automaton is schedulable if there exists a scheduling strategy such that all possible sequences of events accepted by the automaton are schedulable in the sense that all associated tasks can be computed within their deadlines. It has been shown that the optimal schedulability checking problem for such models is decidable and for fixed priority scheduling strategy, the problem can be efficiently solved by reachability analysis on timed automata using only 2 extra clock variables. The analysis can be done in a similar manner to response time analysis in classic Rate-Monotonic Scheduling.

The TIMES tool can be downloaded at <u>www.timestool.com</u>. (It is freely available for research and educational purposes.) It provides a graphical interface for editing and simulation, an engine for schedulability analysis, and a compiler. Given a system design model consisting of

- a set of application tasks whose executions may be required to meet mixed timing, precedence, and resource constraints,

- a network of timed automata describing the task arrival patterns, and

- a preemptive or non-preemptive scheduling policy,

TIMES will generate a scheduler, and calculate the worst case response times for the tasks. The design model may be further validated using a model checker (e.g. UPPAAL) and then compiled to executable C-code using the compiler.

The **Testing** project, which started in the previous period, has in the last years focused on model-based test generation, i.e., automated generation of test suites from a formal design model. The work extends existing techniques for finite-state models in two directions.

- Automated generation of *real-time* tests, which check also quantitative delays) from timed automata specifications, is developed in collaboration with Aalborg University. The generation is guided by supplying test purposes and/or a coverage criterion. Several different coverage criteria are supported. A distinctive feature of our techniques is that for a given test purpose and coverage criterion, a time-optimal (i.e., taking shortest time) test suite can be generated by using an existing extension of UPPAAL to generate optimal test executions.

- Automated generation of tests that consider data parameters using *symbolic* techniques is developed in collaboration with MobileArts AB. Tests are generated from finite state machines extended with boolean data variables. The implementation work has been able to capitalize on other tools developed in the Erlang work of ASTEC. Currently, a protype tool and an evaluation case study are under development.

In the previous period, techniques for translating formal specifications into so-called *test oracles*, i.e., programs that observe the specified system during testing and report when requirements are violated, were developed in a case study in collaboration with Volvo

Technical Development AB. This work has been continued by connecting this generation to the Simulink environment, thus making the oracle generation facility usable by embedded systems engineers.

During 2002 – 2003, the **SMC** project in collaboration with Prover Technology AB has, based on the Prover Plug-in implementation of Stålmarck's algorithm, which in 2000 generated the tool FixIt, focussed on extending the design tool Esterel Scade with the Prover Plug-In to automatically perform fault tree analysis, a wide-spread method for finding minimal combinations of failures of components leading to a failure of the whole system. This allows designers to verify, for example, that it takes at least three components to fail simultaneously to cause the system to become unsafe. The automatic verification is done by repeatedly calling the Prover model-checker. Our implementation extends the Prover Plug-In model checker, We are still improving the tool, which already proved capable of analysing relatively large examples provided by ONERA CERT, Saab AB, and Airbus.

The new **SAAPP** (Simulator-Aided Analysis of Parallel Processes) project develops techniques for analyzing concurrency properties such as data races of programs. To allow analysis of low-level programs, including operating systems and their interaction with user programs, we use and extend the commercially successful instruction-level simulator SIMICS, developed by the industrial partner Virtutech AB. The advantages of SIMICS are that programs run unmodified, and that analysis is done non-intrusively without introducing "probe effects", which are common in earlier approaches which use code instrumentation. We can thus avoid the general problem of abstraction in approaches based on analysis of specifications rather than actual programs. Since SIMICS analyzes programs at a low level of abstraction (essentially machine instructions), techniques must be developed for recovering the process structure of a program, and for detecting the dependencies between processes, communication objects such as locks, semaphores, and shared variables at runtime rather than by using specially instrumented libraries.

#### A.2.4. Programming Language Implementation and Compilation

The area is concerned with the implementation and use of high-level programming languages, together with the development of system software tools such as compilers and program analyzers that enable (time- or space-) efficient execution of programs written in these languages. Activities that also fit in this technical area include compilation techniques tailored to the characteristics of different computer architectures; in particular, compilation techniques for embedded processors.

The biggest project in this area is the **HiPE** project, which focusses on the concurrent functional language Erlang. As mentioned in Section A.2.1, in this period, the project achieved one of its main goals which has been the incorporation of the HiPE native code compiler into the main development and distribution branch of the Erlang/OTP system from Ericsson. The HiPE compiler is an efficient native code compiler for Erlang programs incorporating many optimizations which have been proven successful in the context of functional programming languages. In addition, many other compiler techniques have been adjusted and sometimes developed taking the characteristics of Erlang into account. These include support for concurrency, communication, distribution, fault-tolerance, on-the-fly code reloading, automatic memory management, and preservation of tail-recursion in the context of a mixed mode (i.e., interpreted and native code) execution. In addition, research and development effort was spent in the following directions:

• Initially, the HiPE compiler only generated SPARC code. During this period, a back-end of HiPE for the Intel x86 architecture was designed and developed. A lot of effort was put so that this port reached the level of maturity and robustness that is expected from an industrial-strength compiler which is typically used to develop telecom applications. Results show that the resulting system, HiPE/x86, is significantly faster than the interpreted implementation of Erlang, and achieves speedups comparable to and sometimes better than those of the more mature HiPE/SPARC compiler. This compiler is also included in the Erlang/OTP system and is actively used by the Erlang community.

- The project has investigated compilation techniques for fast, on-the-fly compilation of bytecode into native code (i.e., *just-in-time compilation*). In particular, extensions and improvements to the *linear scan register allocation algorithm* were proposed and experimentally evaluated. For the first time, the quality of allocation obtained by linear scan was measured in the context of a register-poor architecture such as the x86.

- Alternative runtime system architectures for highly concurrent languages were proposed, implemented, and experimentally evaluated. As mentioned in Section A.2.1, one of them, called *shared heap architecture*, is already part of the Erlang/OTP system. For another one, called *hybrid architecture*, a novel static analysis was designed, called *message analysis* that discovers statically the intended use of data (and tracks the program points of their creation) in order to guide the memory allocator.

- Important and useful extensions of the Erlang programming language were designed and developed. In particular, a structured module system (i.e., a *package system* for Erlang) was developed, which has already made it into the Erlang/OTP system and is actively used by many Erlang application programmers. A proposal for a *parameterized module system* has also recently (June 2003) been completed, and work is underway to also include this extension into Erlang/OTP.

The **WPO** (Whole Program Optimization) project develops compiler optimization techniques for embedded systems. The project has thus far primarily focused on two characteristics of embedded systems:

- 1. in embedded systems, memory is an expensive and sometimes limited resource, and thus it is desirable to find techniques that lower the hardware costs by reducing memory usage, and

- architectures for embedded systems are often irregular; sometimes this can be handled by careful redesign of existing algorithms, and sometimes development of new compilation techniques is required.

To reduce the code size of embedded programs, algorithms for code compaction through a technique called *procedural abstraction* were developed and implemented in a prototype. In procedural abstraction, the program control flow graph is scanned for semantically equivalent graph fragments, which are then factored out into a new procedure. The project has investigated the effectiveness and advantages of applying procedural abstraction at the level of intermediate code (as opposed to applying it at the assembly code level). It was found that doing so provides opportunities for more powerful code compaction by e.g., not interfering or be negatively influenced by the effects of register allocation or of other compiler optimization steps.

Embedded systems often have irregular memory architectures; i.e., different memory areas which differ in access time and size. A technique for static allocation of global data to memory areas was developed and benchmarked. The algorithm tries to allocate data so that frequently accessed variables reside in fast memory, and frequently used pointers and pointer expressions are assigned cheap pointer types. Finally, processors used in embedded systems often have an irregular register set; there may for example be register pairs (or other clusters) or non-orthogonal constraints on the operands of certain instructions. We have generalized the standard graph-coloring register allocation to handle such irregularities.

The WCET analysis tool developed within ASTEC contains a flow analysis component. The aim of this analysis is to produce program flow constraints like loop iteration bounds and infeasible path constraints. This information can be used in the subsequent calculation phase to produce a WCET estimate. The analysis can often produce the necessary constraints automatically, without any externally supplied information. The only other WCET tool we know that can do this is the *Bound-T* tool from Space Systems Finland. However, the analysis developed in the context of the **WCET** project places fewer restrictions on the analyzed code to produce useful flow constraints.

The core ideas of the flow analysis were developed in the previous phase of ASTEC and are described in Jan Gustafsson's Ph.D. thesis. The analysis is based on an interval-based

abstract interpretation, operating on the control flow graph of the program just like the classical abstract interpretation by Cousot and Cousot. However, unlike the classical analysis, it works like a symbolic execution. This has consequences for the analysis of loops, where each iteration is analyzed separately rather than approximating the abstract states by widening. This allows for better precision but at the cost of potentially higher time complexity. To curb the complexity, the tool uses *program slicing*. This allows to update only the parts of the abstract states that might change during fixed-point iteration. A syntactical analysis, that screens the code for common, easily-recognized loop patterns with precomputed loop bound formulae, is also under development: the expensive abstract interpretation must then deal only with the remaining, "hard" cases.

The analysis is integrated with the NIC research C compiler also developed within the **WPO** project. It operates on the intermediate code of the compiler, which basically represents the control-flow graph (CFG) of the program after optimizations. This CFG then also represents the program flow in the generated object code, and the flow information is thus valid for WCET calculation for this code. The analysis can handle unstructured code as well as non-recursive function calls. A *pointer analysis* is under implementation and will allow the successful analysis of many programs that manipulate pointers. A first prototype exists and is operational. During the fall of 2003 the tool will be used to evaluate the developed analysis techniques w.r.t. precision and time complexity, for realistic embedded software benchmarks.

#### A.2.5. Real-Time Distributed Systems

This area considers the particular challenges that arise when building embedded real-time and distributed systems. The emphasis is on the needs of software that needs to operate under tight timing constraints and with high requirements for correctness. Analyzing and verifying the timing aspects of a system is the least understood and thus the most difficult part of developing embedded real-time systems. Reliable estimates of computation times are necessary for scheduling and resource allocation, and for analyzing whether a program will meet all deadlines.

The goal of the WCET project is to integrate worst-case execution time (WCET) analysis into a commercial tool for development of embedded systems. The main industrial partners are IAR systems and ENEA Embedded Technology (until recently, OSE Systems). The system and applications are described in Section A.2.2. The WCET project has also produced interesting technical results concerning WCET calculation.

A major problem for WCET calculation is to analyze the program flow to extract information that is not supplied by annotations. This problem was earlier addressed In Jan Gustafsson's Ph.D. thesis. Current work is described in Section A.2.4.

On the hardware side, the timing effect of processor features such as pipelines and caches must be taken into account in order to yield reasonable and safe WCET estimates for a program module. In the Ph.D. thesis of Jakob Engblom, a conceptually simple but powerful technique for analysing the effect of pipelines has been developed. The technique makes it easy to integrate the results of high-level program flow analysis and analysis of cache memories. The technique only depends on having a cycle-accurate simulator for the actual processor available. Hence it can easily be ported to new target architecture, which is very important in the highly fragmented embedded systems processor market. The thesis also contains novel theoretical results, which give criteria under which it is guaranteed that the effects of pipelines are safely taken into account.

The final piece of the WCET puzzle is the combination of the software (program flow) and hardware (pipelines etc.) effects to calculate a WCET estimate. In the Ph.D. thesis of Andreas Ermedahl, several novel and efficient techniques for this step are presented, creating a tool capable of handling complex programs and complex hardware in combination. Three different calculation methods are developed, which trade off speed of calculation against precision of results. In particular, the *clustered calculation method* presented in the thesis combines high precision with high calculation performance, demonstrating excellent scaling for larger programs with many flow facts. This was

previously a potential problem for high-precision constraint-based WCET calculation methods.

#### Some Selected Highlights.

A few of the most interesting achievements in academic research during the period 2001 – 2003 are:

- Results that show how schedulability analysis can be reduced to reachability analysis on timed automata. For fixed priority scheduling, the algorithm uses only 2 extra clock variables (work presented in TACAS'03).

- A detailed description of the pros and cons of different runtime system architectures for concurrent languages and a proposal for a new runtime system architecture (work presented at ISMM'02) on which memory allocation is guided by a novel static analysis called *message analysis* (work presented at SAS'03).

- Fundamental results on execution time analysis for pipelined architectures, described in Jakob Engblom's Ph.D. thesis, and presented at EMSOFT'02.

- Erik Stenman's Ph.D. thesis, titled *Efficient Implementation of Concurrent Languages*, which was conducted in the context of the **HiPE** project, was nominated for the best IT doctoral thesis of 2002 in Sweden.

The following achievements in building tools should be put forward.

- The HiPE native code compiler, which has been fully incorporated into the Erlang/OTP system from Ericsson, and is actively used by the Erlang community.

- An integrated tool for calculating the WCET (Worst-Case Execution Time) of embedded programs with real-time demands.

- The TIMES tool, which received the best tool award at the ETAPS conferences in April 2002.

There are several notable examples of increased involvement of companies in ASTEC, in spite of more difficult economic times.

- A spontaneous cash contribution from T-Mobile, and the subsequent addition of the company as a new (and in fact located outside Sweden!) industrial partner to ASTEC.

- New industrial Ph.D. students have joined ASTEC. There are currently 4 industrial Ph.D. students.

Finally, we would like to mention that

- Uppsala University and its competence centers hosted the NUTEK Competence Center day in 2000.

- A selection of work from ASTEC has been invited and is presented in a special issue of the Springer Verlag journal STTT (Software Tools for Technology Transfer) as an example of establishing a successful co-operation between academia and industry.

## A.3. Scientific Papers

The ASTEC publications can be found in Appendix 7.

## A.4. Examinations

A list of degrees is included at the end of the publication list in Appendix 7.

## A.5. Education and Training

ASTEC has contributed to the development and execution of courses within its areas of interest.

• Upper-level undergraduate and graduate courses have been developed and given on

Testing and Verification, Real-Time Systems, Compiler Techniques, and Theory of Distributed Systems, by senior researchers in ASTEC.

- A national graduate course on modeling and analysis of Real-Time Systems has been developed and conducted, in collaboration with ARTES. A related course has been given to CUGS (The National Computer Graduate School in Computer Science), and to Gävle University.

- ASTEC companies are providing many guest lecturers for undergraduate courses given at Uppsala University and Mälardalen University, which helps in bringing an industrial perspective into university education and are providing students with some impression of the realities of software development practice. For example, senior scientists from Virtutech AB are giving guest lectures on computer architecture, from ENEA are giving guest lectures on software testing, from Prover Technology AB give lectures on formal methods, while scientists from IAR Systems give lectures in Compiler and Real-Time System courses.

- Tools of ASTEC industrial partners, or tools developed in ASTEC projects are used in undergraduate and graduate courses at Uppsala University. For instance, the Simics tool, from Virtutech AB, is used in computer architecture courses. The HiPE, UPPAAL, and TIMES tools are regularly used in undergraduate computer science courses at Uppsala University. The UPPAAL tool is used in undergraduate and graduate courses in a large number of universities world-wide, including Oldenburg University (Germany), Twente University (the Netherlands), IIS (India), University of Pennsylvania (U.S.A.), NUS (Singapore), etc.

The national research programme ARTES which supports research on real-time systems and promotes graduate education, hosted at Uppsala University and funded by SSF (the Swedish Foundation for Strategic Research) with a budget of 88MSEK during 1998-2002, was initiated in 1998 with the support and involvement of several ASTEC researchers. Currently, Prof. Hans Hansson is program director, and he, Parosh Abdulla, and Wang Yi conduct projects funded by ARTES. There is a close coordination between ASTEC and ARTES work: the two bodies share Roland Grönroos as administrator, and several ASTEC projects are closely related to ARTES projects. ARTES++, a graduate school in real-time and embedded systems, was recently granted 7 MSEK in funding from SSF for operation from 2004 to 2006. Some 20 students annually, from 9 participating universities, will be provided support for international mobility, industry contacts, and attending courses. In total, 18 instances of courses will be given. Leadership will be enforced by appointing a director of graduate studies (Paul Pettersson). Support to the ARTES++ graduate school will be instrumental in continued recruitment and education of strong Ph.D. students in the real-time and embedded systems area, and will substantially add to the return on the investment already made in ARTES.

## **B. Standing of the Competence Center in an International and National Context**

## **B.1. Progress of the Centre in Relation to its Long-Term** Goals

#### Background

Industrial and academic collaboration should be particularly relevant for research on software systems: many advances in software technology occur in universities but on the other hand the major part of software production occurs in industry. Such a collaboration thus offers the opportunity for industry to exploit recent advances in software technology and for researchers in academia to evaluate the effectiveness of new techniques in a "real-world" environment.

Though this observation is probably universal, it is particularly applicable to a country like Sweden. Several major products of Swedish industry, e.g., data communication and

process control systems, are to a significant extent based on software. Swedish academia has a strong tradition of research in some areas which have potential applications to software development. The indirect impact of this research on industrial practice, through mobility of individuals and ideas, has been noticeable: functional programming and formal methods have influenced software development in the Swedish telecommunications industry, as witnessed, e.g., by the creation of high-level languages such as Erlang, SDL, and TTCN. ASTEC is intended to build on this tradition, and strengthen direct contacts between academic research and industrial practice, so that advances in academic research can indeed benefit industrial software development, which in its turn can guide the agenda for academic research.

#### **Goals and Strategies**

ASTEC's vision is that, wherever possible, software should be developed using high-level specification and programming languages, supported by powerful automated tools that assist in specification, analysis, validation, simulation, and compilation. ASTECs goals are to contribute to this vision by

- 1. carrying out industrially relevant pre-competitive research at the highest international research level which can be both published in leading scientific conferences and journals and exploited by the industrial parties,

- 2. building up and maintaining a critical-mass, and a concentrated research environment for research, graduate education, collaboration, problem solving, and long-term competence development, and

- 3. being a forum for contact between industrial and academic software researchers.

The strategies chosen by ASTEC to meet these goals are based on the following principles:

- 1. Academic-industrial collaboration and technology transfer require that both parties take an active interest. Therefore, ASTEC work should be conducted with active participation by both industry and academia. Collaboration and a plan for technology transfer will thus be built in from the beginning. This strategy has been successful in building strong links between researchers in academia and in industry.

- 2. Longer-term project planning and the build-up of a concentrated research environment is guided by a *strategic research plan*. The plan structures the challenges addressed by ASTEC into program areas, more precisely described in Section A.

- 3. ASTEC runs and supports seminars and workshops for contact between industrial and academic researchers.

#### History and Evaluations of ASTEC

During the first two years (Phase 1), ASTEC activities focussed on establishing collaboration links between academia and industry by conducting projects where techniques from academia were applied to problems in industry, thereby creating a network of contacts.

To address recommendations of the first ASTEC evaluation, in Phase 2, a *strategic research plan*, which structures challenges for the long-term development of ASTEC, was developed. Based on this plan, more research competence has been recruited and strengthened to build up key areas of ASTEC such as compilation, and the administrative support was strengthened by appointing a research coordinator (Roland Grönroos, 40%). Also in Phase 2, an international *scientific advisory board* was appointed. Currently, it consists of Profs. Neil Jones (DIKU, Univ. of Copenhagen), Bernhard Steffen (T.U. Dortmund), and Neeraj Suri (T.U. Darmstadt). The scientific advisory board has conducted two self-imposed internal reviews in Phase 2 (April 1998 and March 2000), and two in Phase 3 (April 2002 and June 2003). These reviews have pointed out strengths and weaknesses in the technical work of ASTEC, provided guidance, and resulted in shifts of focus of some projects.

The second, mid-term NUTEK evaluation in September 2000 generally expressed its

satisfaction with the work of ASTEC and with the measures taken since the first review. Specific recommendations for individual projects and for the structure of ASTEC in general were made and most of them have been followed during Phase 3. In particular, we mention:

- The recommendation that the ASTEC board be enriched with influential leaders from industry partners. In the current period, Catrin Hansson-Granbom (from Ericsson AB) and Jan Lindblad (from OSE Systems AB) joined the ASTEC board, and an assisting director was appointed.

- That procedures and mechanisms be developed that ensure that all researchers and participants are well informed about projects, technology tranfer plans, and the interrelationships between projects. In response to this recommendation, ASTEC has created the **CODER** project cluster, organized half-day long seminars where work from the three technical areas of ASTEC was presented in a concentrated form (in addition to the annual ASTEC research meetings), and has kept the frequency of meetings between project leaders (where the progress of individual projects is discussed) high.

#### Progress

Within Uppsala University, ASTEC is recognized as an important long-term strategic research unit. In written and oral presentations of research in information technology, ASTEC is referred to as a strong pillar of research in Computer Science, and as an example of successful and continued establishment of collaboration between academic researchers with industry.

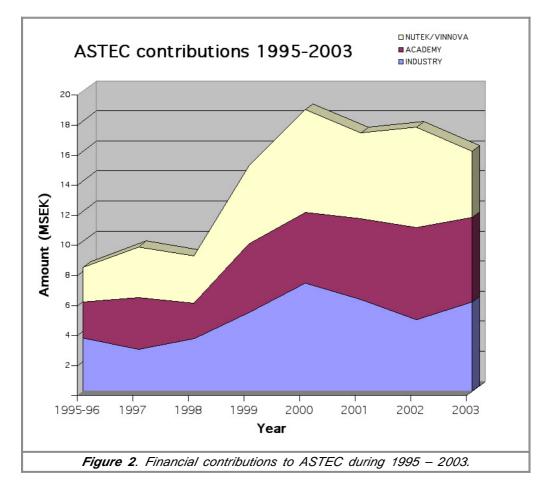

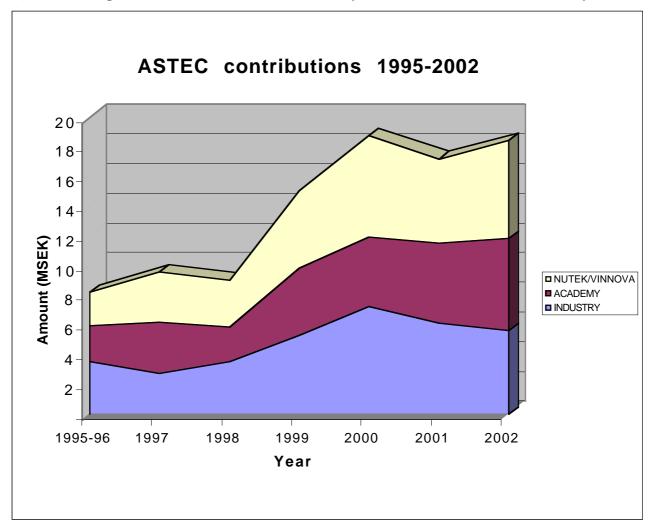

Over the years, the participation of industry within ASTEC has been steadily increasing. The number of companies involved within ASTEC has grown from 6 to 12 in 2002 and 14 in 2003; see data shown in Table 2 below. As a rather unusual "success-story" we mention the inclusion of a non-Swedish company (T-Mobile) as parner of an ASTEC project in 2003. Results from ASTEC work have been transferred and are nowadays used in industry. Despite the difficult times for companies in the information technology sector, financial contribution from industrial partners of ASTEC has reached its peak in 2000 and has kept at a high level during the last few years.

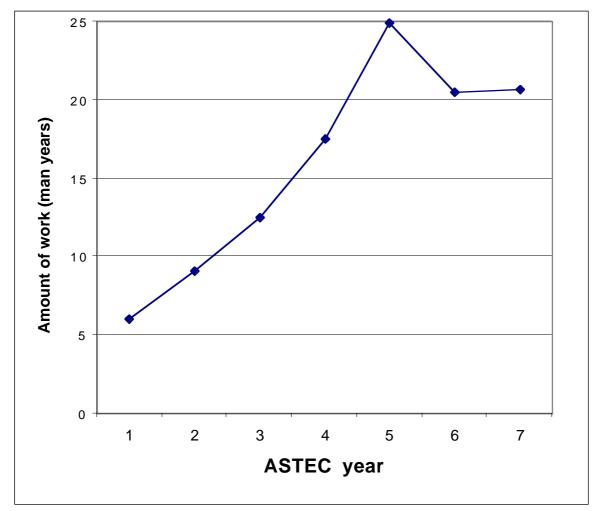

The production of graduates (Ph.D., Lic. and M.Sc.) has acquired momentum (a total of 5 till 1999, 15 in 2000, to a total of 27 at the end of 2002). The centre has graduated one and currently employs four industrial Ph.D. students. ASTEC researchers and graduates have moved to the industrial partners of ASTEC, and some ASTEC researchers also have part-time appointments with companies. The centre has developed and conducted graduate courses in its area of competence, and its seminar series is continuing in full speed during the last few years.

## **B.2. International and National Collaboration**

ASTEC researchers are firmly established in the international research community. Senior researchers are members of program committees in key conferences of the areas of the strategic research plan. For 2001-2003, these include

- ACS (Int. Conf. on Applications of Concurrency to System Design),

- CAV (Conference on Automated Verification),

- CC (Compiler Construction),

- CONCUR (Conference on Concurrency Theory),

- FEMSYS (Formal Design of Safety Critical Embedded Systems),

- ICFEM (Int. Conf. on Formal Engineering Methods),

- ICALP (Int. Colloquium on Automata, Languages and Programming),

- ICLP (Int. Conf. on Logic Programming),

- LICS (IEEE Symp. on Logic in Computer Science),

- LCTES (Languages, Compilers, and Tools for Embedded Systems),

- NWPT (the Nordic Workshop on Programming Theory),

- PPDP (ACM SIGPLAN Principles and Practice of Declarative Programming), where

Konstantinos Sagonas was Conference Chairman in 2003,

- RTCSA (Int. Conf. on Real-Time Computing Systems and Applications),

- RTSS (IEEE Real Time Systems Symposium),

- SEFM (Int. Conf. on Software Engineering and Formal Methods)

- TACAS (Tools and Algorithms for the Construction and Analysis of Systems), where Prof. Wang Yi was Program co-Chairman in 2001.

A sign of recognition is that the TIMES tool received the best tool award at the ETAPS conferences in April 2002, and that ASTEC has been invited to present its activities in a special issue of the Springer Verlag journal STTT (Software Tools for Technology Transfer).

ASTEC has a strong network of international contacts. As examples, the UPPAAL and TIMES projects have been collaborating very closely with Aalborg University in Denmark since 1995. ASTEC groups have had a long been an active collaboration with Seoul National University (SNU) (Andreas Ermedahl (then an ASTEC Ph.D. student) has been on a 6 month visit at SNU), and with C-Lab in Paderborn, Germany (including frequent visits by Friedhelm Stappert)

In addition to visits within the collaboration just mentioned, ASTEC attracts both long- and short-term visitors. Prof. Werner Damm, Univ. of Oldenburg, has spent a semester as visiting professor in autumn 2001. ASTEC groups host several post-doc researchers (currently 4) from other countries.

Through its partners, ASTEC participates in several European Community research projects.

- WOODDES (Workbench for Object Oriented Design and Development of Embedded Systems), concluded in 2003, is devoted to development technology for embedded systems in automotive and telecommunication industry within the framework of UML. The project has 6 European industrial partners and 2 academic partners: Oldenburg University, Germany and Uppsala University.

- The ARTIST (Advanced Real Time Systems) project, in which Mäardalen University and Uppsala University participate, collects around 20 leading research groups in Europe with the objectives to coordinate European Research and Development effort in the area of Advanced Real-time Systems, e.g., by identifying innovative and relevant research directions.

- The ADVANCE (Advanced Validation for Telecommunication Protocols) project, develops tools that extend the power of formal analysis. Its partners include Uppsala and Ericsson.

- The GAMES Research and Training network GAMES, comprising 7 European and 1 U.S. University is concerned with developing techniques for the synthesis and validation of computing systems that are based on games and automata.

- PROFUNDIS (Proofs of Functionality for Mobile Distributed Systems) focusses on formal modelling and verification techniques for key issues in mobile distributed systems, such as security authentication, access rights and resource management. The 4 academic partners include Uppsala University.

- <u>ESACS</u> (Enhanced Safety Assessment for Complex Systems) aims at developing new tools and methodologies to improve safety analysis of complex systems. Partners include 4 aircraft industries and several reseach centers, including Prover Technology AB, Sweden.

Our participation in all these projects builds directly on ASTEC work.

SAVE (Component Based Design of Safety Critical Vehicular Systems) is a national project supported by SSF (Swedish strategic research). The goal of the project is to establish an engineering discipline for systematic development of component-based software for safety critical embedded vehicular systems. Uppsala's effort within SAVE will be focused on component models and verification of quantatative properties of components.

ASTEC has co-organized and co-sponsored several international workshops and conferences, including PLI'03 (Principles, Logics and Implementations of High-Level

Programming Languages) which comprises of ICFP (ACM SIGPLAN International Conference on Functional Programming), PPDP (ACM SIGPLAN Conference on Principles and Practice of Declarative Programming), and a total of five co-located workshops.

A collection of scientific papers, which represent ASTEC work, has been invited and will be published in the Springer Verlag journal STTT (Software Tools for Technology Transfer), together with a cover paper which presents the ASTEC framework, with the goal of presenting ASTEC to a wider scientific community.

ASTEC conducts technical seminars, and seminars directed to an industrial audience. For example, Jakob Engblom gave a lecture on efficient C programming for embedded systems, on behalf of IAR Systems, at the Embedded Systems Conferences in San Francisco in 2001 and 2002. The lecture topic was how to write code that is efficiently compiled by a modern C compiler. Open half-day seminars are organized to present results of selected ASTEC project clusters. A concentrated seminar presenting the Erlang work was organized on 14 November 2002, and a seminar on the CODER work was organized on 12 March 2003.

### **B.3. Core Competences and Critical Mass**

Over the years, ASTEC has developed into a focussed research unit with a critical mass within the technical areas of the centre: verification and validation, (declarative) programming languages and compilation, and development of techniques and tools for real-time and embedded systems. Within these areas, ASTEC performs research on the highest international level. Impressive recognized research results have been produced, of both theoretical and practical nature, which are published in leading conferences and journals of the field. ASTEC collaborates with other national research initiatives, and has strong international collaboration links, including links with several big European Community research projects.

The companies also contribute to the centre's research profile. Several companies, which are industrial partners of ASTEC, are world-leading suppliers of technology for software development, and are thus also on the frontier of international research in the areas of relevance. As examples, Prover Technology AB owns what may be the world's most powerful solver for satisfiability problems, which is now integrated into the Esterel Scade tool. Enea Embedded Technology develops the OSE Real Time Operating System, one of the most popular RTOS's. Virtutech AB, with its SIMICS product, is the world leader in the design and development of full system simulation platforms. Software tools produced by research conducted under the aegis of ASTEC are being used by big international companies of the telecom industry such as Ericsson and T-Mobile.

Cooperation between academic and industrial units of ASTEC has become closer and more interconnected within this period.

- As an example, the work on projects involving Erlang has resulted in regular, bi-monthly day-long meetings between members of the HiPE (at UU) and Erlang/OTP (at Ericsson) development teams. There has also been a collaboration between the Failure analysis project and the AXD-301 development team at Ericsson. Finally, the Failure analysis tool used and provided feedback for software tools developed within the context of the HiPE project.

- Another example of close coordination between different activities in ASTEC is the formation of the **CODER** (Cluster on Distributed and Embedded Real-Time systems) cluster, which originated from integration of the **WCET** group with the **WPO** group, and which also includes the projects **TAS** and **Remodeling**. The rationale for forming the **CODER** cluster is that there are obvious synergies between research on compilation techniques for embedded systems and research on execution-time analysis of code for such systems. In practice, this has worked out very well. There is a research compiler infrastructure shared by the two groups, and there have been several joint graduate seminars on program analysis techniques. The work in the **CODER** cluster is geographically and organizationally dispersed, with nodes at Uppsala University, IAR Systems, CC-Systems, ABB, OSE Systems AB, and

Mälardalen University. There is also a steady cooperation with C-Lab in Paderborn, Germany. This has worked well, thanks to using email, instant messaging programs, and the use of CVS (Concurrent Versions System) to share text and code.

• Finally, links between industry and academia are often strengthened by the fact that ASTEC researchers are appointed jointly by academia and industry and by the increasing number of industrial Ph.D. students.

## B.4. Role and Impact of the Centre within the University

Over the last several years, Uppsala university has taken several measures in order to increase the visibility and operational efficiency of its educational and research programs in the information technology field. In January 1999 the various small departments dealing with different aspects of IT were joined to two large departments, and the Virtual IT-faculty was created to coordinate and promote the role of IT within the university in different ways. These reforms have now been consolidated and we can see a very strong IT-department which offers a good administrative infrastructure for large research programs and good opportunities for collaboration between different specialties within the IT field. Generally speaking, ASTEC has been part of this increased focus on the IT area within the university both in the sense that the program has had advantages from it and that the activities within ASTEC have been seen as part of the focus on IT at Uppsala University.

Malardalen University has over the last several years developed MRTC (the Mälardalen Real-Time REsearch Centre) into a strong environment for Real-Time research, now with around 70 researchers. A recent development was the creation, in January 2003, of SEL (Software Engineering Laboratory), a research laboratory, focusing on

- Software engineering for industrial, real-time and embedded systems; this will include the engineering technologies, tools, and processes.

- Component-based software engineering.

The staff of SEL contains two professors, 4 lecturers, and around 12 Ph.D. students.

In the late nineties, IT saw a very strong expansion both in terms of number of programs and courses and number of student positions. During the last two years, the recruitment of undergraduate students has been negatively affected by the problems in the IT sector. This has affected all Universities and University Colleges including Uppsala. In the case of Uppsala, we have been able to handle the decreased interest without major problems and the number of full time students at the department now seems to stabilize around 1000. The recruitment to Ph.D. studies has actually benefited from the current situation. It is now even easier to attract good students to the Ph.D. programs. This has been clearly noticed also in the ASTEC program.

ASTEC is formally a separate administrative unit within Uppsala University. The administration is hosted in the IT Department but the accounting is separated from that of the department. One of the beneficial effects of the formation of a joint IT-department is that we now have a very strong administration, it is probably the best of all departments within Uppsala University. The department is organized with a common administrative unit for the whole department, and there are senior professional administrative persons responsible for every key task with good back up possibilities. Therefore the capability to manage and coordinate large projects is very good.

The structure of the IT Department is exceptionally well suited for centers such as ASTEC also from an academic point of view. It is unique for Swedish Universities that expertise representing the whole chain from data collection, signal processing, automatic control, advanced software development, database engineering, and numerical analysis are all available within one department. For development of advanced industrial software this is an excellent environment that is not yet fully utilized to its full potential.

In several of these areas the department has been successful in attracting world-leading experts. The number of professors at the IT Department has increased from 8 to 22

since its creation in January 1999. Several of the new chairs at Uppsala University (and also Mälardalen University) are in areas that support ASTEC work, including real-time systems, computer architecture, computer communications, and computing science. ASTEC has indirectly catalyzed the creation of some of these chairs. The most recent additions of professors in areas closely related to ASTEC are Erik Hagersten in Computer architecture and Stefan Seipel in Computer graphics and visualization. Hagersten has taken a seat on the ASTEC board and new industrial collaborations have been formed involving Hagerstens group and ASTEC.

Uppsala University has over the last few years carried out a major strategic planning and resource reallocation process called BASTU (SAUNA). One of the outcomes of that process was significant new resources to High performance computing through the establishment of a new centre UppMAX which will have a handful of senior application experts that support researchers wishing to use or develop high performance computing. This opens up several new potential collaboration areas for ASTEC.

ASTEC is together with a few other strategic research programs always presented as an important part of the research strategy of the university. ASTEC is frequently mentioned in accounts of the research program in Computer Science at Uppsala University. Examples include the STUNS report, and presentation of Research in IT to representatives of the leadership of research at SUN, ABB, Ericson, Volvo Car Corp, and other major companies in ASTEC related areas.

## C. Industrial Benefits, Technology Transfer, Impact to the Industrial Partners

## C.1. Industrial Involvement and Interaction

The industrial involvement in ASTEC has continuously increased with about one partner per year since the center started in 1995; see Table 2. What is not shown in the table is the fact that the industrial involvement is particularly strong on the level of individuals: many companies have reorganised and changed names during the period, but the involved personal contacts have been increasingly strong and expanding.

|                                                                             |       | Year |      |      |      |      |      |      |      |      |

|-----------------------------------------------------------------------------|-------|------|------|------|------|------|------|------|------|------|

|                                                                             | all   | 2002 | 2002 | 2001 | 2000 |      | 1998 | 1997 | 1996 | 1995 |

|                                                                             | years | 2003 | 2002 | 2001 | 2000 | 1333 | 1330 | 1331 | 1330 | 1995 |

| ABB Automation                                                              |       |      | 1    | 1    | 1    | 1    |      |      |      |      |

| Products AB                                                                 |       |      |      |      |      |      |      |      |      |      |

| ABB LtD                                                                     |       | 1    |      |      |      |      |      |      |      |      |

| Cross Country<br>Systems AB                                                 |       | 1    | 1    | 1    |      |      |      |      |      |      |

| Ericsson Radio<br>Systems AB                                                |       |      |      |      |      |      |      | 1    | 1    | 1    |

| Ericsson Telecom<br>Systems AB<br>Ericsson<br>Utvecklings AB<br>Ericsson AB |       | 1    | 1    | 1    | 1    | 1    | 1    | 1    |      |      |

| ESAB Welding                                                                |       | 1    | 1    | 1    |      |      |      |      |      |      |

| Equipment AB                                                                |       |      |      |      |      |      |      |      |      |      |

| I.A.R. Systems AB                                                           |       | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| Mecel AB                                                                    |       |      |      |      | 1    | 1    | 1    | 1    | 1    | 1    |

| Mobile Arts AB*                                                             |       | 1    |      |      |      |      |      |      |      |      |

| ENEA OSE Systems<br>AB                                                      |       |      | 1    | 1    |      |      |      |      |      |      |

| OSE Systems AB**                                                            |       | 1    |      |      |      |      |      |      |      |      |

| Prover Technology<br>AB                                                     |       | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| Rational Software<br>Scandinavia AB                                         |       |      |      |      |      |      | 1    | 1    | 1    | 1    |

| T-mobile Inc.*                                                              |       | 1    |      |      |      |      |      |      |      |      |